We are digital implementation team inside Siemens. Our mission is to integrate latest process technology with most updated commercial design content (CPU, GPU, DSP, etc.) to demonstrate expected performance, power, and area (PPA) improvement. Our results and developed flows are references for worldwide 1st tier design houses.

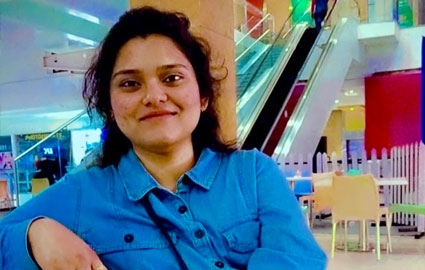

Name

Age

Occupation

Company

Place

Education

Bhavana Maddu

25 Years

Application Engineer

Siemens EDA

Portland, OR USA

MS in Electronics

Height

Weight

Phone

Nationality

Visa Type

5'4" / 162.56 cm

70 kgs / 154.324 lb

+1 971-428-4577

Indian

H1-B (USA)

Years of

Experience

Academic

Projects

Total

Projects

8005 Boeckman Rd, Wilsonville, OR 97070, United States

Webew Technologies Pvt Ltd, Bharathpet, Guntur

Webew Technologies Pvt Ltd, Bharathpet, Guntur

My educational journey has had good and challenging experiences. For the most part, my educational journey was positive.

1825 SW Broadway, Portland, OR 97201, Phone: 503-725-3000

Chowdavaram, Guntur, Andhra Pradesh, 522019, INDIA.

Sri Chaitanya Junior College, Dhana Lakshmi campus, Guntur

Master's in Electrical & computer engineering, specialization in Design verification & validation track

Designing a synthesizable RPN Calculator (Reverse Polish Notation) and verifying it with a UVM based testbench environment.

Training and Hands-on experience in Verilog and Digital Design. Applied concepts like Verification flow, Self-Checking testbench, Randomization, Synchronous FIFO, Verilog Design and Verification.

Functional Verification, Gate Level Simulation, Building modular, reusable testbenches, implementing coverage-driven verification, and leveraging transaction-level modeling in system Verilog, Very-Large-Scale Integration

She is my first friend, my best friend, and my forever friend. My sister is my treasure, the women that keep me grounded. My sister and I, we are just like a really small gang.

Sister

My daughter is my biggest achievement. She is a little star and my life has changed so much for the better since she came along. In my life, you are the sun that never fades and the moon that never wanes.

Mother

There is this girl who stole my heart and she calls me Daddy. Behind every great daughter is a truly amazing dad. Being a daddy’s girl is like having permanent armor for the rest of my life.

Father

8520 sw Ash meadows rd, Apt 1428, Wilsonville, Oregon, 97070